Sony se joint FDSOI Club, EE Times

MADISON, Wis -. Sony Corp. a révélé que la puce de nouvelle génération de l'entreprise système mondial de navigation par satellite (GNSS) utilisera 28 nm Fully Depleted Silicon On Insulator processus (FDSOI).

La société japonaise a utilisé 28nm STMicroelectronics kit de conception de FDSOI et fabriqué ses échantillons FDSOI à la fab ST.

Tout en arrêtant à court d'annoncer une date de lancement pour la puce, la société japonaise partagée au forum son propre FDSOI « expérience de conception », ce qui lui donne la place d'un pouce. L'orateur Kenichi Nakano de Sony a présenté un exposé intitulé « conception de faible puissance SOC avec le circuit RF par le 28nm FDSOI. »

Un représentant STMicroelectronics a dit EE Times, « FDSOI est plus seulement une histoire plus ST. » Si le Forum SOI est une mesure, l'écosystème FDSOI vient ensemble. Parmi les autres présentateurs Samsung, VeriSilicon, Open Silicon, Synopsys et Cadence. Ils ont rapporté leurs propres résultats et IP avec FDSOI.

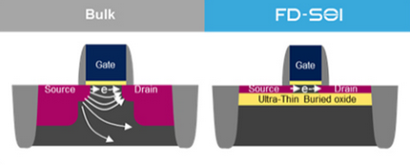

FD-SOI permet de meilleures caractéristiques électrostatiques de transistors par rapport à la technologie classique en vrac. La couche d'oxyde enterrée diminue la capacité parasite entre la source et le drain.

Pour réduire la consommation d'énergie pour la puce GNSS, Nakano indiqué avoir tout de RF, la logique et SRAM sur la puce fonctionnant à 0,6 V, au lieu de 1.1V.

L'équipe de Nakano a essayé le processus FDSOI 28nm, testé la faisabilité de la conception et a confirmé qu'elle peut atteindre tous les objectifs de performance en utilisant l'évaluation du groupe de test Element (TEG).

directeur principal de VeriSilicon de l'ingénierie, Shirley Jin, qui a déclaré que son entreprise dispose d'un portefeuille de propriété intellectuelle dans une vaste 28nm FDSOI, le flux de conception de travail et de l'infrastructure pour exécuter les dessins, résume l'expérience de conception de VeriSilicon dans sa présentation.

Appel FDSOI « une technologie économe en énergie », a déclaré Jin, « actions 28nm de FDSOI la plupart des mêmes dispositifs que processus en vrac, et permet le portage de conception facile. » Le 28nm FDSOI permet un compromis de conception flexible pour l'alimentation / performances et offre bon usage des techniques corps-biais. Par exemple, Polarisation du corps (FBB) peut améliorer encore les performances, tout en Polarisation inverse du corps (RBB) peut réduire les fuites.

C'est mon à ce long fil 2-cts.

Rang de l'utilisateur

Auteur

Sang Kim, vous avez maintenant fait ce même poste à plusieurs reprises, et ont déjà été répondu à chaque fois montrant exactement où vos affirmations sont wriong (mise à l'échelle ITRS, épaisseur SOI, etc.). Si vous ne pouvez pas comprendre les réponses il n'y a pas de point de poursuivre ce fil.

Rang de l'utilisateur

Auteur

FDSOI n'est pas extensible. Comment épaisseur SOI ultraminces est nécessaire

pour 14nm FDSOI? Moins de 4 nm. 4Nm est considéré comme le

fin de la mise à l'échelle selon la RTRS parce que 3 nm, 2 nm, 1 nm

ne sont plus soumis à la physique de l'appareil classique, au lieu soumis à des effets de confinement quantique mécaniques structurelles

résultant en augmentation de Vt, une grande variation de transfert électrique

des caractéristiques telles que Vt, la pente sous le seuil, did / dVg,

did / DvD. etc. Ou sujet à l'incertitude.

Pourriez-vous indiquer mes cinq faux « faits », selon votre

compte pour que je puisse répondre?

Rang de l'utilisateur

Auteur

Les présentations de Samsung montrent que 28FDSOI est une meilleure performance - en particulier la puissance plus faible - et le coût similaire ou inférieur par mourir que 28nm en vrac, si vous ne croyez pas cela, alors demandez-vous pourquoi ils iraient à tous les efforts de mise en place d'un tel processus ? Comme il a été dit à plusieurs reprises, le coût de la tranche augmentation est compensée par un traitement plus simple (moins masques / étapes), et il est le traitement où la plupart des coûts de plaquette va.

Le fait que 14nm FDSOI est pas dans la production mais ne montre pas qu'il est pas échelonnable, il montre juste qu'il est retardé par rapport à FinFET - comme cela a été FDSOI 28nm par rapport à 28nm en vrac. Comme AKH0 continue de vous dire, l'épaisseur de départ SOI est> 10nm ce qui est parfaitement et a été fabricable depuis plusieurs années, a terminé l'épaisseur SOI même pour le nœud de 10 nm est 5 nm, ce qui est aussi très bien. Vos chiffres sont tout simplement faux, les longueurs de grille ne sont pas les mêmes que le « nœud de processus » (comme il est très bien connu), et vos épaisseurs de SOI sont beaucoup plus petites que la réalité.

Les gens continuent à vous dire d'aller lire sur le sujet parce que vous continuez à afficher le même faux « faits » (par exemple sur la longueur de grille, l'épaisseur du substrat, fabricabilité, mise à l'échelle, le coût) encore et encore; même quand il a fait remarquer que vos « faits » sont fausses et où trouver les bonnes, vous rediffuser toujours à nouveau les mêmes (maintenant au moins cinq fois selon mes calculs). Ce n'est pas une question d'opinion ou d'un débat, votre soi-disant « faits » sont tout simplement faux.

Rang de l'utilisateur

Auteur

28nm transistors planaires en vrac sont fabriqués pour le volume

plusieurs années par les grandes sociétés de semi-conducteurs tels

comme Intel, TSMC, Samsung, GF et d'autres, mais 28nm SOI ou

la technologie FDSOI dispositifs à base ne sont pas fabriqués encore

par les grandes sociétés de semi-conducteurs. Pourrais-tu me dire

Pourquoi? À moins 28nm FDSOI montre de meilleures performances et

a moins les coûts de fabrication par rapport à 28nm en vrac,

28nm FDSOI ne sera pas fabriqué parce qu'une plaquette SOI

les coûts seuls 4 ou 5 fois plus élevé que d'une tranche simple et

peut-être aussi les coûts de traitement plus élevés. Il semble que le débat est

Je n'ai pas les questions anti-FDSOI / pro-FinFET. Au contraire, je voudrais

comme d'avoir des problèmes de raboteuse en vrac 28nm FDSOI / 28nm parce que

FinFET 22nm et 14nm sont dans la production de masse sur deux

années par Intel et FinFET de 16nm fabriqués cette année par

TSMC, mais de FDSOI n'est pas fabriqué à 22nm, 16nm et

14nm nœuds encore. Ainsi, il montre FDSOI n'est pas contraire évolutive

à FinFET parce que sur 5 nm, 4 nm, et environ 3 nm SOI

épaisseurs nécessaires pour 22nm, 16nm et 14nm FDSOI

les appareils ne sont pas fabricable. 4Nm est considéré comme le

fin de la mise à l'échelle selon la RTI.

Comme je l'ai dit précédemment, ce n'est pas un forum pour me dire qui

devrait être mon professeur ou votre professeur et quels papiers

et des livres de texte à lire ou à utiliser les mots comme « FUD sans fin ».

Ce n'est pas la première fois. Je vous ai dit jamais comme ça dans

ici les deux points de vue sur FDSOI. Je voudrais entendre spectateur de

avis sur la technologie FDSOI. C'est tout.

Rang de l'utilisateur

Auteur

« Supposons maintenant que les (trous) sont collectés par la source comme

opposition à collectés par le puits MOSFET en vrac, Qu'est-ce que

mal est fait? » Le mal est fait grand courant de fuite

provenant de la polarisation directe N + (source) P (trous)

diode comme barrière induite par trou d'abaissement comme DIBL,

dégrader les performances du MOSFET, même l'échec.

premier finFET 22nm d'Intel a été développé et

fabriqué pour supprimer le courant de fuite. 28nm ou

30nm est raboteuse en vrac non finFET. Les structures d'ailettes

y compris à haute ailette, la largeur ailette à la partie inférieure et la grille

longueur de finFET 22nm d'Intel ont été déterminées par MET

section transversale non seulement par Intel et d'autres se conformant t

il longueur de grille égale à 22 nm, non 30nm. Je ne suis pas tout à fait

comprendre pourquoi TSMC appel 16nm finFET au lieu de

30nm finFET. 30nm appartient à la raboteuse en vrac, non

Encore une fois, je voudrais entendre de tout coeur votre

point technique de vues, y compris les désaccords, mais

franchement n'aiment pas entendre votre conseille, comme ce

papiers à lire, combien de temps je devrais lire, qui

conférences j'assister. etc. Ce n'est pas votre

un dernier vient de poster ici.